征信查詢(xún)管理系統(tǒng) 信息系統(tǒng)集成服務(wù)的重要支撐

征信查詢(xún)管理系統(tǒng)是金融機(jī)構(gòu)及相關(guān)部門(mén)進(jìn)行信用信息采集、查詢(xún)與管理的核心平臺(tái),而信息系統(tǒng)集成服務(wù)則是確保其高效運(yùn)行的關(guān)鍵所在。本文將從需求背景、集成內(nèi)容、服務(wù)優(yōu)勢(shì)以及發(fā)展趨勢(shì)等方面展開(kāi)分析。

隨著數(shù)字經(jīng)濟(jì)時(shí)代的到來(lái),信用體系在社會(huì)經(jīng)濟(jì)活動(dòng)中的作用日益凸顯。征信查詢(xún)管理系統(tǒng)通過(guò)整合多源數(shù)據(jù),實(shí)現(xiàn)對(duì)個(gè)人及企業(yè)信用狀況的綜合評(píng)估,不僅為銀行、保險(xiǎn)等機(jī)構(gòu)提供決策依據(jù),還助力構(gòu)建社會(huì)誠(chéng)信體系。系統(tǒng)的復(fù)雜性、數(shù)據(jù)安全要求高以及與其他業(yè)務(wù)系統(tǒng)的兼容性問(wèn)題,使得信息系統(tǒng)集成服務(wù)成為不可或缺的一環(huán)。

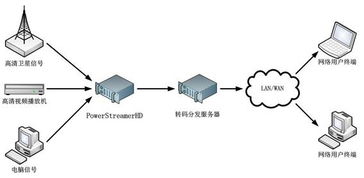

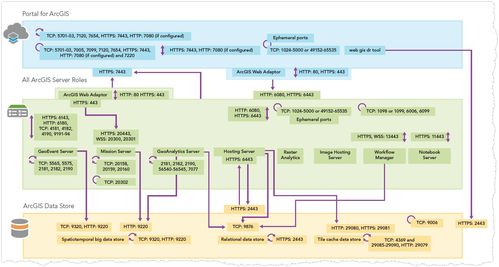

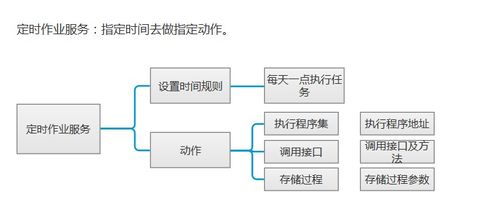

信息系統(tǒng)集成服務(wù)在征信查詢(xún)管理系統(tǒng)中涵蓋多個(gè)層面。硬件集成涉及服務(wù)器、存儲(chǔ)設(shè)備及網(wǎng)絡(luò)設(shè)施的部署與優(yōu)化,確保系統(tǒng)具備高可用性和可擴(kuò)展性。軟件集成包括操作系統(tǒng)、數(shù)據(jù)庫(kù)以及應(yīng)用軟件的整合,例如將征信查詢(xún)模塊與風(fēng)險(xiǎn)控制、客戶(hù)管理等系統(tǒng)無(wú)縫對(duì)接,實(shí)現(xiàn)數(shù)據(jù)共享與流程自動(dòng)化。數(shù)據(jù)集成是關(guān)鍵環(huán)節(jié),通過(guò)ETL工具和數(shù)據(jù)標(biāo)準(zhǔn)化處理,消除信息孤島,提升查詢(xún)效率與準(zhǔn)確性。安全集成也不容忽視,需采用加密技術(shù)、訪(fǎng)問(wèn)控制和審計(jì)機(jī)制,保護(hù)敏感征信數(shù)據(jù)免受泄露和濫用。

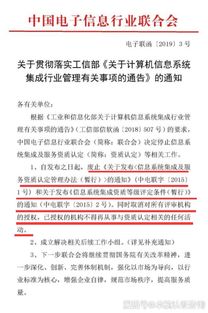

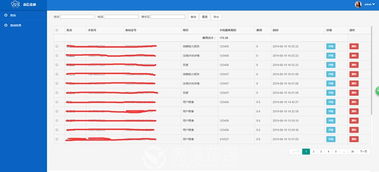

專(zhuān)業(yè)的信息系統(tǒng)集成服務(wù)為征信查詢(xún)管理系統(tǒng)帶來(lái)顯著優(yōu)勢(shì)。它能夠降低系統(tǒng)建設(shè)與維護(hù)成本,通過(guò)標(biāo)準(zhǔn)化接口和模塊化設(shè)計(jì),縮短開(kāi)發(fā)周期。集成服務(wù)提升了系統(tǒng)的穩(wěn)定性和響應(yīng)速度,支持大規(guī)模并發(fā)查詢(xún),滿(mǎn)足金融機(jī)構(gòu)實(shí)時(shí)業(yè)務(wù)需求。從用戶(hù)體驗(yàn)角度,集成的系統(tǒng)界面更友好,操作更便捷,有助于提高工作效率。更重要的是,集成服務(wù)確保了合規(guī)性,幫助機(jī)構(gòu)遵循相關(guān)法規(guī)如《征信業(yè)管理?xiàng)l例》,避免法律風(fēng)險(xiǎn)。

征信查詢(xún)管理系統(tǒng)的集成服務(wù)將向智能化與云化方向發(fā)展。人工智能與大數(shù)據(jù)技術(shù)的融入,將使系統(tǒng)具備更精準(zhǔn)的風(fēng)險(xiǎn)預(yù)測(cè)能力;而云計(jì)算平臺(tái)則提供彈性資源,支持系統(tǒng)快速擴(kuò)展。隨著跨境數(shù)據(jù)流動(dòng)的增加,集成服務(wù)需加強(qiáng)國(guó)際合作與標(biāo)準(zhǔn)統(tǒng)一,以應(yīng)對(duì)全球化挑戰(zhàn)。

信息系統(tǒng)集成服務(wù)是征信查詢(xún)管理系統(tǒng)成功實(shí)施的基石。通過(guò)全面的技術(shù)整合與優(yōu)化,它不僅保障了系統(tǒng)的高效安全運(yùn)行,還推動(dòng)了社會(huì)信用體系的建設(shè)。金融機(jī)構(gòu)和相關(guān)單位應(yīng)重視集成服務(wù)的選擇與投入,以充分發(fā)揮征信數(shù)據(jù)的價(jià)值。

如若轉(zhuǎn)載,請(qǐng)注明出處:http://www.dzdv63.cn/product/14.html

更新時(shí)間:2026-04-08 18:17:02